4000频率内存时序

- 内存

- 2024-04-13 06:18:27

- 8019

内存时序是指访问和操作内存数据所需的时钟周期数量。 对于 4000 频率内存,时序通常表示为 CL-tRCD-tRP-tRAS,其中:

CL (CAS 延迟):从发出读取命令到返回数据的时钟周期数。

tRCD (行到列延迟):从发出行命令到发出列命令之间的时钟周期数。

tRP (行预取时间):在发出新行命令之前,需要等候的时钟周期数。

tRAS (行激活时间):保持行激活状态所需的时钟周期数。

对于 4000 频率内存,常见的时序包括:

CL18-22-22-42

CL16-20-20-38

CL14-18-18-36

时序重要性

内存时序会影响内存的整体性能,包括读写速度和延迟。 较低的时序通常表示更快的内存,因为数据可以更快地访问。

例如,CL14-18-18-36 时序的内存比 CL18-22-22-42 时序的内存具有更低的延迟,这将导致更快的性能。

选择内存时序

选择 4000 频率内存的时序时,有以下几个因素需要考虑:

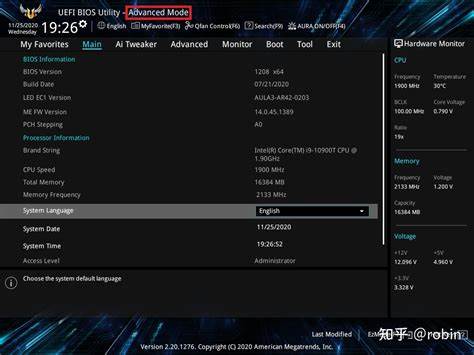

处理器:不同处理器的内存控制器可能支持不同的时序。

主板:主板也可能限制支持的时序。

预算:时序较低的内存通常比时序较高的内存更昂贵。

用途:对于要求高性能的应用程序或游戏,时序较低的内存更加合适。

总体而言,较低的 4000 频率内存时序可提供更好的性能,但可能需要支付更高的成本。 根据特定需求和预算,选择合适的时序至关重要。

上一篇:内存频率4000选g1还是g2

下一篇:4000频率内存时序c19高吗